Für eine Unterstützung mehrerer RTE-Protokolle ist Flexibilität bei der Umsetzung in einer Kommunikationsanschaltung gefordert. FPGA (Field-programmable Gate Arrays) sind flexible, leistungsfähige und preiswerte Bauelemente, die durch das Laden von IP-Cores an die konkrete Anwendung (z.B. als Ethernet-Kommunikations-Schnittstelle) angepasst werden. Die Echtzeitlösungen der RTE-Protokolle werden ebenfalls durch IP-Cores umgesetzt. Zusammen mit weiteren IP-Cores lassen sich flexible Lösungen für die Integration von Ethernet in Feldgeräte erstellen. Wie das unter Verwendung des Cyclone III von Altera möglich ist und welche Vorteile der Nutzer von dieser Lösung heute und in Zukunft hat, erläutert der folgende Artikel. Zugriff auf Echtzeitdaten Für den Zugriff auf Echtzeitdaten unter Nutzung von Ethernet haben sich mehrere Systeme etabliert, die unterschiedliche Anforderungen erfüllen. Ethercat, Ethernet/IP und Profinet gehören zu den relevanten Systemen und haben sich am Markt durchgesetzt. Ein Hersteller von Feldgeräten (Sensoren, Aktoren, Drives, Remote-I/O usw.) muss diese Protokolle unterstützen, um in verschiedenen Industrien und auf verschiedenen geographischen Märkten präsent und erfolgreich zu sein. Zwei Punkte sind hierbei wichtig: – Optimales Unterstützen der verschiedenen RTE-Protokolle mit einer Anschaltung und – Zukunftssicherheit für die Integra- tion von Weiterentwicklungen und neuen Anforderungen ohne Ände- rung der Hardware. Eine FPGA-basierte Lösung erfüllt beide Anforderungen. Der FPGA-Baustein wird durch das Laden verschiedener IP-Cores an seine konkrete Aufgabe angepasst. Für einen IP-Core werden die gewünschten Eigenschaften eines Bausteins in einer entsprechenden Sprache definiert und in eine Struktur miteinander verschalteter Logikelemente übersetzt. Es gibt IP-Cores für verschiedene Schnittstellen (UART) oder für den Zugriff auf externe Speicher. Mit dem Nios II steht für Alteras Cyclone III-Familie ebenfalls eine Softcore-CPU bereit. Auch hier unterstützen IP-Cores die verschiedenen Real-Time Ethernet-Protokolle. Während des Hardware-Designs wird festgelegt, welche konkreten IP-Cores zur Abarbeitung der Anwendung benötigt werden, wie sie miteinander verbunden werden und wie die Kommunikation mit anderen Bausteinen (Speicher, Peripherie) erfolgt. Diese Information wird dann in einem Speicherbaustein in definierter Weise hinterlegt und zur Laufzeit über eine vorgeschriebene Ablauffolge geladen. Ändern sich in Zukunft Spezifikationen und Anforderungen, so wird ein neues Hardware-Design erstellt und auf der Hardware hinterlegt. Ein aufwendiges Redesign der Hardwareanschaltung, weil z.B. ein neuer Prozessor mit geänderter Pin-Belegung eingesetzt werden muss, ist nicht notwendig. Weiterentwicklungen Wichtig ist weiterhin, dass mit dem Cyclone III-FPGA ein jedes Jahr millionenfach gefertigter Baustein zur Verfügung steht. Dadurch ist eine Partizipation an Weiterentwicklungen in der Mikroelektronik gesichert. Es handelt sich bei der vorgestellten Lösung nicht um einen proprietären Asic mit fest verdrahteten Funktionen eines Herstellers aus der Automatisierungsbranche, sondern um das Produkt eines großen Halbleiteranbieters, das für einen bestimmten Einsatzfall konfiguriert wurde. Bild 1 zeigt das Hardware-Design für den Altera Cyclone III mit 40k Logikelementen, das für die Unterstützung verschiedener RTE-Protokolle optimiert ist. Es beinhaltet einen Baustein mit RTE-Hardware-Support. Im Bild ist ein Switch mit zwei externen und einem internen Port gezeigt, wie er für Profinet und Ethernet/IP relevant ist. Es kann aber ebenso der IP-Core für den Ethercat-Slave genutzt werden. Dem internen Mac ist die Ethernet-Adresse des Gerätes zugeordnet. Das Gegenstück befindet sich im Nios II. Der Austausch zwischen interner Mac und Gegenstück im Nios II erfolgt nicht über Ethernet, sondern über einen FIFO-Speicher. Weiterhin gehören eine Nios II Softcore-CPU für die Abarbeitung der Protokoll-Software, ein DP-RAM, ein Speicher-Interface sowie weitere Schnittstellen-Cores zum Design. Ein zusätzlicher Nios kann für das Abarbeiten von Anwendungs-Software genutzt werden. Eine Hardware ohne ein entsprechendes Betriebssystem ist in vielen Fällen nicht ausreichend. Für den Altera Cyclone III sind mehrere Betriebssysteme verfügbar. Für den besprochenen Einsatzbereich sind sicherlich die beiden Systeme eCos und Linux interessant. Sie sind beide lizenzkostenfrei, und es gibt eine große Unterstützer-Gemeinde. Bei eCos handelt es sich um ein schlankes Betriebssystem, das aber dennoch wichtige IP-Anwendungen (z.B. SNMP) mit an Bord hat. Mit Linux steht ein System bereit, das den Zugriff auf weitere Protokolle und Anwendungen auch im Ethernet/TCP/IP-Umfeld ermöglicht. Security sei hier als ein Beispiel genannt. Softing bietet für eCos Profinet IO als Device entsprechend Conformance Class B und Ethernet/IP mit den Funktionen eines Adapters an. Eine Integration von Ethercat mit Slavefunktionalität befindet sich in der Entwicklung. Neben der einheitlichen Hardware-Schnittstelle zum Ethernet, die durch die verschiedenen IP-Cores realisiert wird, existiert eine durchgängige Software-Schnittstelle zur Anwendung. Das Simple Device Application Interface bietet immer die gleiche Funktionsschnittstelle für die Anwendung – unabhängig vom genutzten RTE-Protokoll. Der Anwender des Konzeptes kann die im Weiteren vorgestellten Wege bei der Integration des Ethernet-Anschlusses in sein Gerät gehen. Integrationsmodell 1 Im ersten möglichen Integrationsmodell entwickelt der Gerätehersteller eine eigene Hardware auf der Basis des Altera Cyclone III. Er wird dies dann tun, wenn er über eigene IP-Cores z.B. für die optimale Ansteuerung von Motoren verfügt. In diesem Fall bietet das Evaluation-Kit von EBV einen Einstieg für eine erste Evaluierung. Hier erhält er neben dem Board auch die Entwicklungsumgebungen für das eigene Hardware- und Software-Design. Das oben erwähnte Betriebssystem und die Stacks laufen auf dem Evaluation-Board. Auch die benötigten IP-Cores sind verfügbar. Eine Prüfung der Stack-Funktionen im Zusammenspiel mit weiteren Geräten und einer prototypischen Integration in das Zielgerät ist möglich. Bei Akzeptanz der Lösung schließt sich die Entwicklung an. Der Prozess ist in Bild 2 dargestellt. Die benötigte Hardware und Software kommt von verschiedenen Lieferanten. Neben eigenen IP-Cores kommen IP-Cores von Altera und Cores zur Umsetzung der RTE-Protokolle zum Einsatz. Integrationsmodell 2 Besteht keine Notwendigkeit für ein eigenes FPGA-Design, so bietet Softing ein entsprechendes Integrations-Paket an. Dabei wird ein vorgefertigtes Real-Time Ethernet Module (RTEM) mit installierter Hardware-Konfiguration, Stacks und Betriebssystem geliefert. Das Modul ist im Bild 3 gezeigt. Zu diesem Paket gehört weiterhin die Entwicklungsumgebung für Software. Der Anwender kann eigene Programme für die Geräte-Integration entwickeln. Hat sich der Kunde nach der Evaluierung für die Lösung entschieden, so hat er mehrere mögliche Umsetzungsvarianten: – Unmittelbare Integration des RTEM – Redesign gemäß entsprechender Anforderungen (anderer Formfak- tor o.Ä.) Die Tabelle 1 beschreibt für die unterschiedlichen Integrationsmodelle jeweils die Aufgaben für den Kunden und Softing. RTE- & Standard-Anwendungen Neben den RTE-Protokollen kann auf dem Modul auch Standard-TCP/IP mit den entsprechenden Anwendungen realisiert werden. Hierfür bietet sich ein zweiter Nios-II-Core an, auf dem dann Linux läuft. Somit stehen viele Standard-Protokolle zur Verfügung. Durch das Verwenden eines zweiten Cores lassen sich die Datenpfade logisch voneinander trennen, wie im Bild 4 dargestellt. Der Switch verfügt über zwei interne Ports. Somit hat das Gerät zwei Ethernet-Adressen und kann zwei unabhängige IP-Adressen haben. Eine Remote-Maintenance-Anwendung kann völlig unabhängig von der Echtzeitdaten-Kommunikation genutzt werden. Vorteile des FPGA-Einsatzes Bei FPGA handelt es sich um elektronische Bauelemente, die durch Laden verschiedener IP-Cores an eine entsprechende Aufgabe angepasst werden. Die Leistungsfähigkeit eines FPGAs wird auch durch die Anzahl der Logikelemente (LE) beschrieben. In Abhängigkeit von der Anzahl der IP-Cores und deren Größe können unterschiedliche FPGAs zum Einsatz kommen. Diese können Pin-kompatibel sein. Der Cyclone III mit 25kLE und der Cyclone III mit 40kLE sind voll Pin-kompatibel. Es kann also wahlweise ein Design mit einem Nios oder mit zwei Nios umgesetzt werden. Damit kommt bereits der große Vorteil des FPGA – seine Flexibilität zum Ausdruck. Durch die Massenfertigung und Fortschritte in der Produktion sind FPGA heute kaum teurer als Asics. Im Unterschied zu diesen sind sie aber von Abkündigungen nicht betroffen. Die IP-Cores sind in VHDL beschrieben. Somit können sie mit jeder neuen FPGA-Generation wieder verwendet werden. FPGAs gehen sparsam mit Energie um. Ein Cyclone III mit dem Design aus Bild 4 benötigt 0,6W. Die erwähnte Profinet-Lösung erreicht Zykluszeiten von 1ms. Durch die Verfügbarkeit von leistungsfähigen Betriebssystemen und Entwicklungssystemen sind FPGA auch auf diesen Gebieten Mikroprozessoren gleichwertig.

Flexible Kommunikationsanschaltung: Integration von Echtzeit-Ethernet in Feldgeräte

-

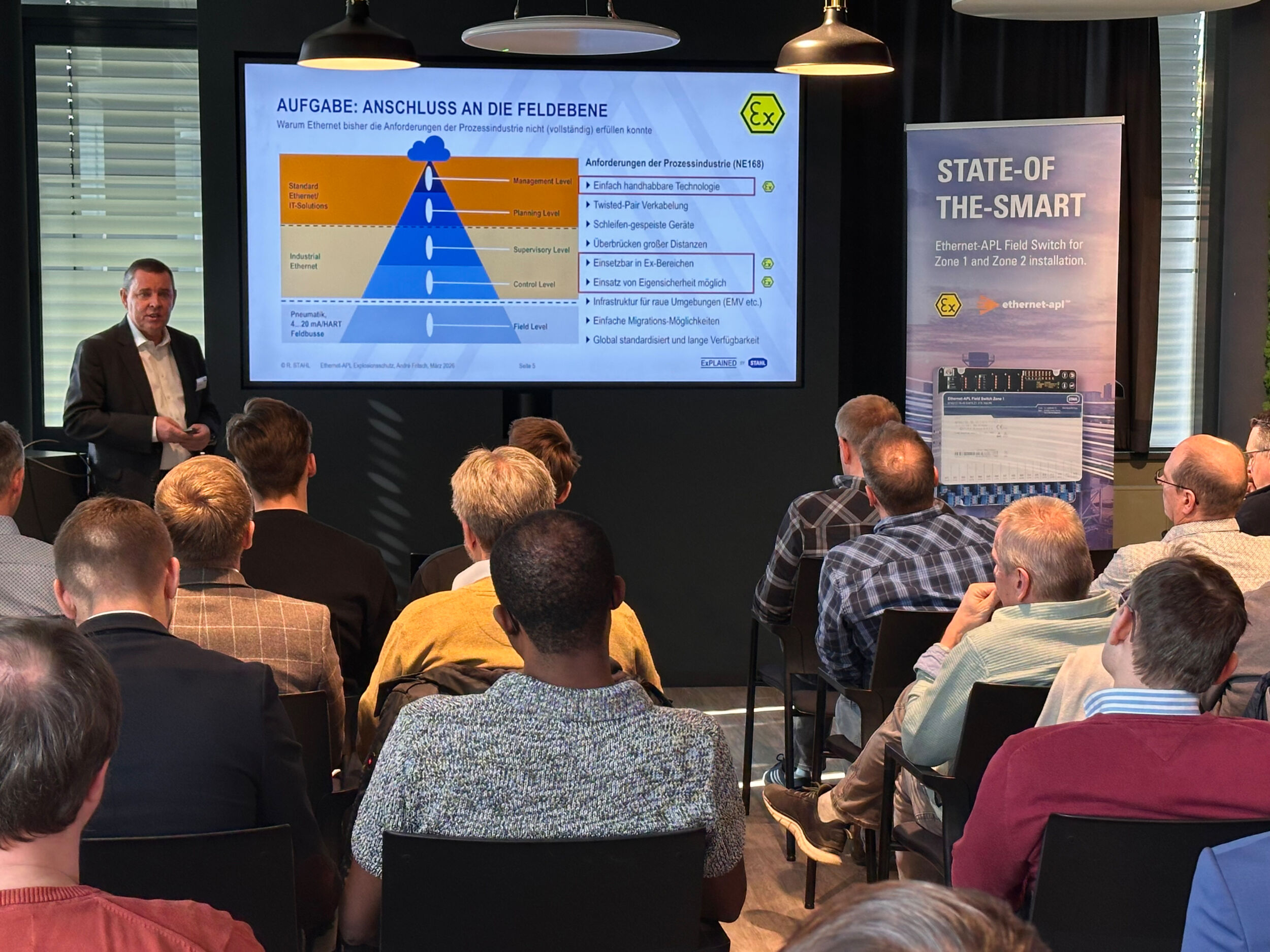

Digitale Prozesse: Mit Ethernet-APL sicher und effizient

Die Digitalisierung der Prozessindustrie schreitet unaufhaltsam voran – und sie stellt neue Anforderungen an die Kommunikationsinfrastruktur.

-

Elektromechanisches Fügesystem

Kistler hat mit dem IJSys ein neues Fügemodul entwickelt, das alle Komponenten inklusive Servoantrieb, Sensor, Digitalisierung von Daten und Sicherheitstechnik im Modul selbst vereint.

-

Infrarotsensor regelt Materialauftrag bei der Plasmabeschichtung

Ultradünne Barriereschichten auf Verpackungen können Lebensmittel oder Medikamente wirksam vor Kontakt mit Sauerstoff, Feuchtigkeit oder Schadstoffen schützen.

-

Neues Mitglied im Wago Management Board

Zum 1. Mai verstärkt Jens Hunecke das Management Board bei Wago als Chief Business Officer des Geschäftsbereichs Interconnection.

-

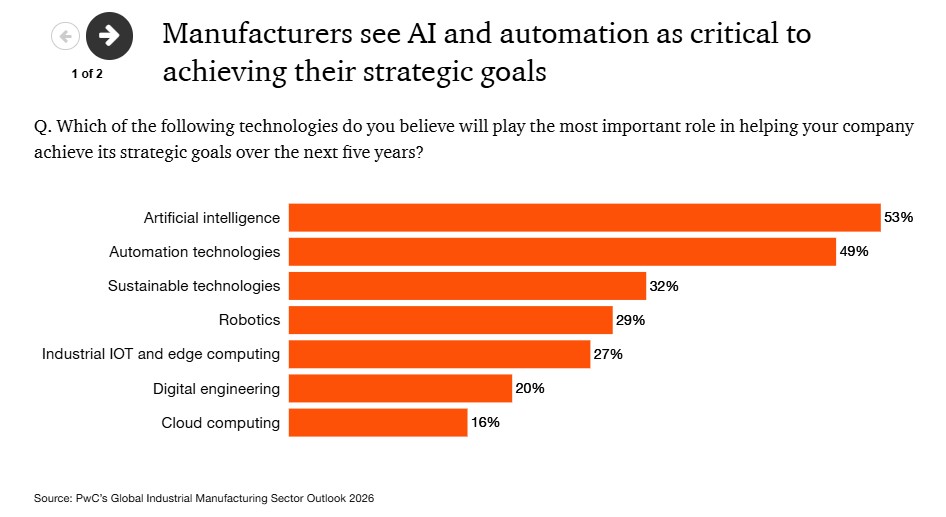

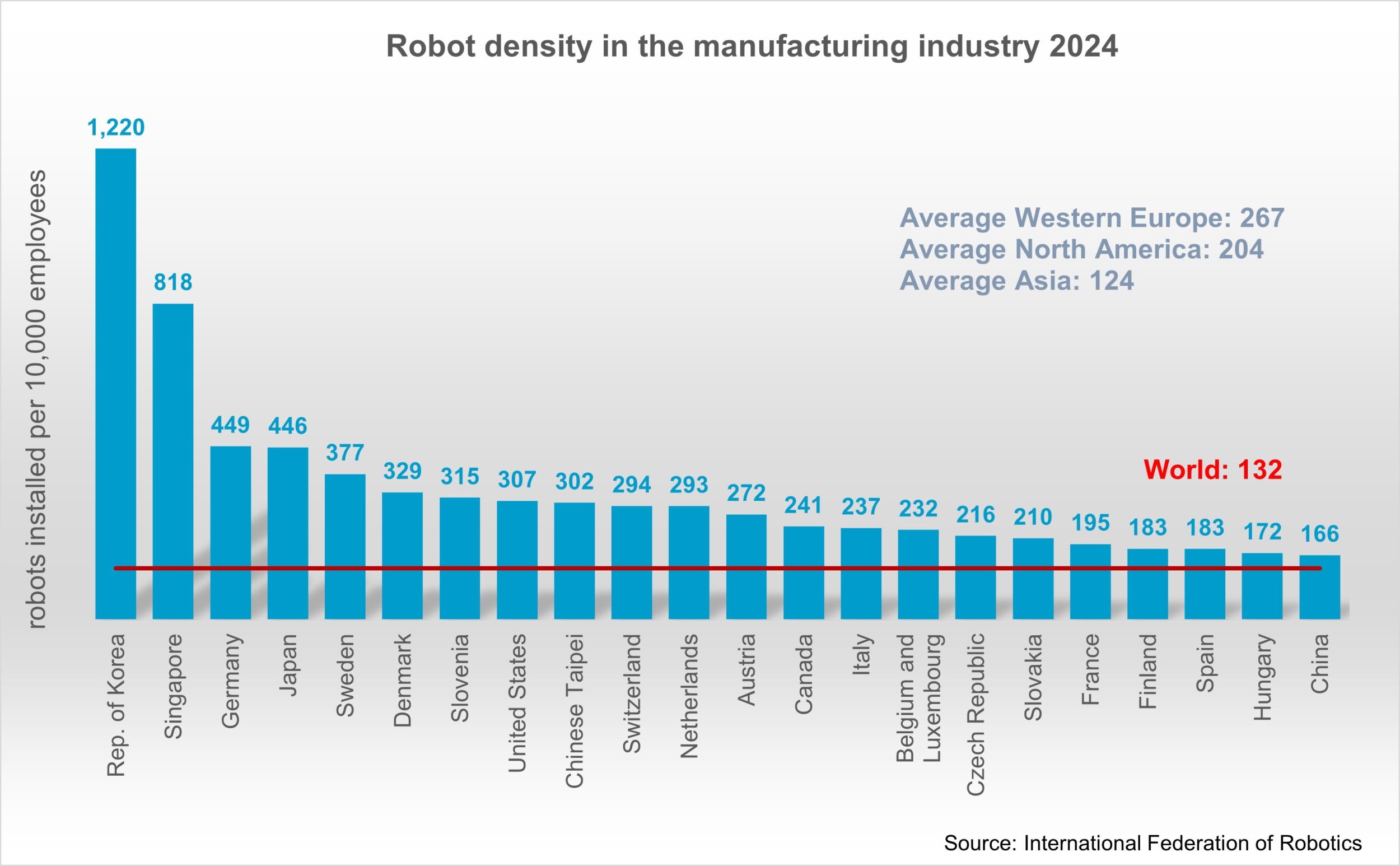

Roboterdichte steigt in Europa, Asien und Amerika

Westeuropa installierte 2024 im verarbeitenden Gewerbe einen Rekord von 267 Industrierobotern pro 10.000 Arbeitnehmern und führt damit im internationalen Automationsrennen vor Nordamerika mit 204 Einheiten und Asien mit…

-

CiA-Vorstand wieder gewählt

Auf der Vollversammlung des Vereins CAN in Automation wurde der amtierende Vorstand bestätigt:…

-

Schmersal gehört 2026 zu den besten Arbeitgebern in Nordrhein-Westfalen

K.A. Schmersal zählt 2026 zu den besten Arbeitgebern in Deutschland.

-

Komplexe Bewegungen über High-Level-Sprachen steuern

Es geht auch ohne Echtzeit

Die koordinierte Bewegung mehrerer Achsen – z.B. bei Robotikanwendungen – ist kein neues…

-

Offizielle Eröffnung der Hima-Niederlassungen in Kolumbien und Peru

Die Hima Group baut die Präsenz in Lateinamerika mit der offiziellen Eröffnung neuer…

-

Maßgeschneiderte Schwingungsüberwachung mit IO-Link

Gemeinsam zur Lösung

Steigende Anforderungen an die Überwachung von Schwingförder- und Siebmaschinen erfordern präzise und flexibel…

-

Kompakter Distanzsensor bis 150m

Mit dem OptoNCDT ILR1041-150-IO erweitert Micro-Epsilon sein Laser-Distanzsensoren-Portfolio um ein kompaktes Modell für…

-

Gute Ergänzung

Der SCHALTSCHRANKBAU und das Thema ’schaltschranklose Automatisierung‘: Wie passt das denn zusammen? So…

-

Wenn Unmanaged Switches Managed Funktionen übernehmen

Plug&Play trifft Priorisierung

Netzwerksegmentierung und Datenflusspriorität sind in der industriellen Automatisierung keine Kür mehr, sondern Pflicht.…

-

Skalierbare IPC-Plattform

Spectra bietet mit der MD-3000-Serie von Cincoze eine modulare Embedded-Computer-Plattform an, die speziell…

-

Retrofit für die Industrie 4.0

So lassen sich alte Steuerungen wirtschaftlich OPC-UA-fähig machen

Viele Produktionsanlagen arbeiten noch mit Steuerungen, die seit Jahrzehnten zuverlässig ihren Dienst verrichten.…

-

KI perfektioniert Phishing-Angriffe – von personalisierten Mails bis zu Voice Cloning

Wenn Maschinen Vertrauen imitieren

Die KI generiert nicht nur immer neue Hacker-Tools, sondern verbessert die Glaubwürdigkeit von…

-

Interview: Wie neue EU-Regularien Maschinenbauer zu sicheren Kommunikationsarchitekturen zwingen

„Cybersecurity ist heute keine Option mehr“

Mit neuen regulatorischen Vorgaben wie dem Cyber Resilience Act steigt der Druck auf…

-

IO-Link-Safety-Lösungen

Mit der Kombination robuster Sicherheitskomponenten und IO-Link Safety ermöglicht Euchner eine durchgängige, sichere…

-

Im Interview: Wie NI und DataTec den europäischen Testmarkt neu denken

Vom Messgerät zur Datenplattform

Beim Besuch von National Instruments bei DataTec tauschten sich Ritu Favre, President Test…

-

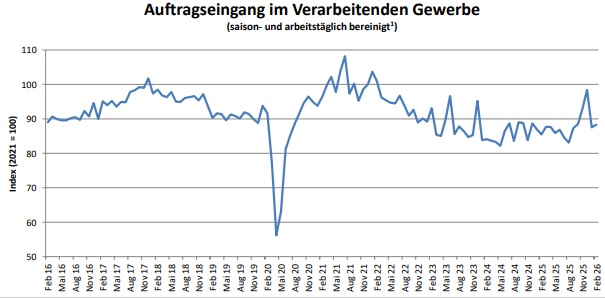

Spürbarer Dämpfer in den Bestellungen

Maschinenbau-Auftragseingang im Februar

Der Auftragseingang im Maschinenbau ist im Februar abermals gesunken und die Stimmung der…

-

Für die DACH-Region

Schneider Electric: Neuer Vice President Secure Power

Schneider Electric hat Marco Geiser zum neuen Vice President Secure Power DACH ernannt.

-

Yaskawa strukturiert Führungsspitze in Europa um

Yaskawa hat eine Neustrukturierung der Geschäftsführung in seiner europäischen Zentrale vorgenommen.

-

ABB Robotics ernennt neuen Cluster-Manager für DACH-Region

ABB Robotics hat Marc-Oliver Nandy zum Cluster-Manager für die DACH-Region ernannt.

-

Für sichere Maschinennetzwerke

Industrial Security-Gateway und Maschinenfirewall

Sichere Maschinennetzwerke werden mit den aktuellen Vorgaben der Europäischen Maschinenverordnung und der IEC62443…

das könnte sie auch interessieren

-

-

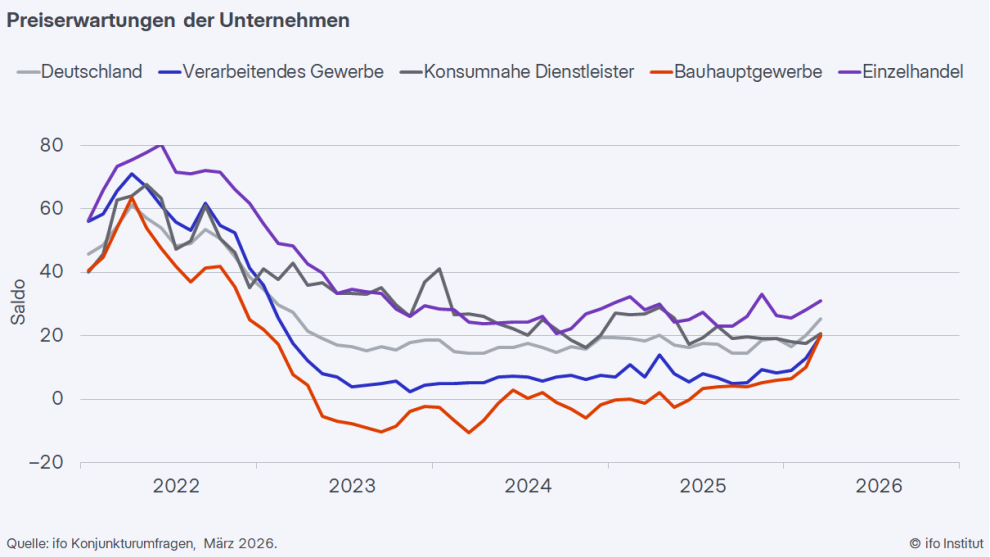

Ifo-Konjunkturumfrage

Unternehmen planen mit höheren Preisen

-

Ann Fairchild neue CEO

Siemens USA unter neuer Leitung

-