Ein weiterer Evolutionsschritt im Bereich der PACs war die Integration der benutzerdefinierbaren Onboard-FPGA-Technologie. Field-Programmable Gate Arrays (FPGAs) sind als rekonfigurierbare Siliziumchips vielseitig einsetzbar und in der Lage, hohen Anforderungen in Bezug auf Determinismus, geringe Latenzzeit, Parallelität, Verarbeitungsgeschwindigkeit und Zuverlässigkeit gerecht zu werden. Generell erfreut sich die FPGA-Technologie im Bereich von computerbasierten Mess- und Automatisierungsanwendungen immer größerer Beliebtheit. Seit Xilinx im Jahre 1984 die ersten FPGAs auf den Markt brachte, hat sich die Technologie von einfachen Schnittstellenchips stetig weiterentwickelt, so dass moderne FPGAs als Ersatz für fest vordefinierte ASICs (Application-Specific Integrated Circuits) und Prozessoren in Signalverarbeitungs- sowie Steuer- und Regelanwendungen genutzt werden. Vollständig rekonfigurierbar Grob gesagt, handelt es sich bei FPGAs um wiederprogrammierbare Siliziumchips. Diese Chips beinhalten eine Matrix bestehend aus Millionen von Logikblöcken, welche durch programmierbare Routen verknüpft werden können. Dadurch lassen sich auch komplexere Algorithmen wie z.B. FFT-Analysen oder PID-Regelkreise auf Basis von digitalen Logikschaltungen realisieren. Somit bieten FPGAs, genauso wie fest vordefinierte ASIC-Chips, den Vorteil, dass eine anwenderdefinierte Funktionalität, losgelöst von jeglicher Beschränkung durch Betriebssysteme und CPU-Taktung, autark in Hardwaregeschwindigkeit zuverlässig abgearbeitet wird. Zudem haben FPGAs gegenüber ASICs den Vorzug, dass die zu integrierende Intelligenz durch Software vordefiniert und in Form eines Bit-Files auf den FPGA eingeprägt wird. Somit sind FPGAs vollständig rekonfigurierbar und können sofort neue \’Aufgaben\‘ annehmen, sobald eine andere Schaltungskonfiguration in Form eines Bit-Files kompiliert wird. Anders ausgedrückt, vereinen FPGAs die besten Eigenschaften von ASICs und prozessorgestützten Systemen. Wiederprogrammierbare Siliziumchips sind genauso flexibel wie Software, die auf einem Prozessor ausgeführt wird. Ihre Leistungsfähigkeit wird jedoch nicht von der Anzahl der verfügbaren Prozessorkerne eingeschränkt. Im Unterschied zu Prozessoren ermöglichen FPGAs tatsächlich parallele Ausführung, so dass verschiedene Verarbeitungsoperationen nicht auf die gleiche Ressource angewiesen sind. Jeder einzelne Verarbeitungs-Task wird einem dedizierten Bereich auf dem Chip zugewiesen und kann so autonom und ohne Beeinflussung anderer Logikblöcke ausgeführt werden. Auf Grund dessen wird die Leistungsfähigkeit der Anwendung nicht eingeschränkt, wenn weitere Verarbeitungs-Tasks hinzugefügt werden. Vereinfachte FPGA-Programmierung Bisher stand FPGA-Technologie nur den Anwendern zur Verfügung, die über fundiertes Wissen im Bereich digitales Hardwaredesign und der VHDL-Programmierung verfügten. Der verstärkte Einsatz von abstrahierenden Designwerkzeugen wie z.B. LabView vereinfacht auch die FPGA-Programmierung, da neue Technologien in der Lage sind, grafische Blockdiagramme oder sogar C-Code in digitale Hardwareschaltungen zu konvertieren. Das PAC-System CompactRio basiert auf der oben beschriebenen FPGA-Technologie und ergänzt die PAC-Plattform von National Instruments genau um dieses Konzept. Dieses Embedded-Echtzeitsystem vereint in kompakter Form die Vorteile eines PC-basierten Echtzeitcontrollers mit der Leistungsfähigkeit der FPGA-Technologie. Zur Realisierung der Anwendung ermöglicht das NI LabView FPGA Module die Erstellung der Algorithmen, die direkt auf dem FPGA-Chip abgebildet und dort ohne den Overhead eines Betriebssystems in echtem Hardware-Timing ausgeführt werden. Der angeschlossene Controller erlaubt die Abarbeitung von LabVIEW-Real-Time-Anwendungen und verfügt über eine Vielzahl von Kommunikationsschnittstellen, wie u. a. Ethernet, Ethercat, Profibus, Canopen, Serial und USB. Zudem ermöglichen die über 100 verfügbaren C-Serien-Module ganz einfache analoge und digitale I/O bis hin zu direkter und Aktor- (z. B. Motoren) und Sensoranbindung durch integrierte Signalkonditionierung im Modul. Die Architektur des CompactRio bringt eine hohe Flexibilität hinsichtlich Timing, Triggerung und Synchronisation mit sich. Zudem lassen sich Regelalgorithmen realisieren, die sonst nur mittels teurer eigener Hardwareentwicklung möglich sind. \’Intelligente\‘ Erweiterungschassis Die NI-CompactRio-Technologie lässt sich aber nicht nur mit den integrierten Echtzeitcontrollern nutzen. Es ist auch möglich, den FPGA-basierten I/O-Teil in Form eines Erweiterungschassis einzusetzen. Dies empfiehlt sich z.B. bei Anwendungen mit dezentral verteilter I/O. Oftmals genügt es lediglich, die \’intelligenten\‘ Erweiterungschassis in Verbindung mit einem zentralen Controller zu verwenden. Derzeit sind Erweiterungschassis mit unterschiedlicher Steckplatzanzahl und Bus-Anbindung verfügbar. MXI-Express Rio Die MXI-Express-Rio-Erweiterungschassis (9159) mit 14 Steckplätzen können mit jedem kompatiblen Controller über eine x1-MXI-Express-Verbindung kommunizieren. Jedes dieser Chassis verfügt über zwei MXI-Express-Anschlüsse, damit mehrere Chassis mit dem gleichen Controller in Reihe geschaltet werden können. Über einen MXI-Express-Bus und einen leistungsstarken FPGA sind diese Chassis am besten für lokale Steuer-, Regel- und Überwachungsanwendungen mit hohen Geschwindigkeiten geeignet, die eine Datenübertragung für viele Kanäle und die Implementierung benutzerspezifischer Messungen mit einer datenintensiven Verarbeitung erfordern. Ethernet Rio Das robuste Ethernet-Chassis (NI 9148) mit acht Steckplätzen eignet sich für die Erstellung von dezentralen I/O-Systemen. Es kommuniziert über Standard-Ethernet mit jedem beliebigen Desktop- oder Industrie-PC. Aufgrund dieser Flexibilität ist das Chassis NI 9148 eine gute Wahl für die nahtlose Integration von I/O-Erweiterungen an bestehende Netzwerktopologien. Durch die Verwendung des integrierten FPGAs können benutzerspezifische Mess-, Steuer- und Regelungsaufgaben direkt vor Ort und nahezu latenzfrei durchgeführt werden. Ethercat Rio Das Ethercat-Slave-Chassis (NI 9144) mit acht Steckplätzen erlaubt die Kommunikation über das deterministische Ethernet-Protokoll Ethercat. Es ist am besten für dezentral verteilte Steuer- und Regelanwendungen geeignet, die exakten Determinismus für mehrere, synchronisierte Chassis erfordern. Anwender setzen deterministische Ethernet-Protokolle für die Strukturüberwachung von Windturbinen, synchronisierte Prüfstände sowie Steuer- und Regelanwendungen über große Entfernungen ein. Grafische Programmiersprache Für die Programmierung der CompactRio-Plattform eignet sich die grafische Programmiersprache NI LabView. LabView hat sich mittlerweile zum De-facto-Standard im Bereich der Mess- und Prüftechnik entwickelt. Seine intuitive grafische Programmiermethodik, die Flussdiagrammen ähnelt, bietet die Funktionalität einer vollwertigen Programmiersprache und eine benutzerfreundliche Oberfläche. Durch die Module LabView Real-Time und LabView FPGA werden ein Echtzeitbetriebssystem und die Möglichkeit, FPGAs direkt anzusprechen, miteinander verbunden. Damit lassen sich auf sehr intuitive Weise hochleistungsfähige Steuer- und Regelsysteme auf Basis der PAC-Technologie realisieren. embedded world 2011: Halle 10, Stand 221

FPGA-Technologie in der Automatisierungstechnik

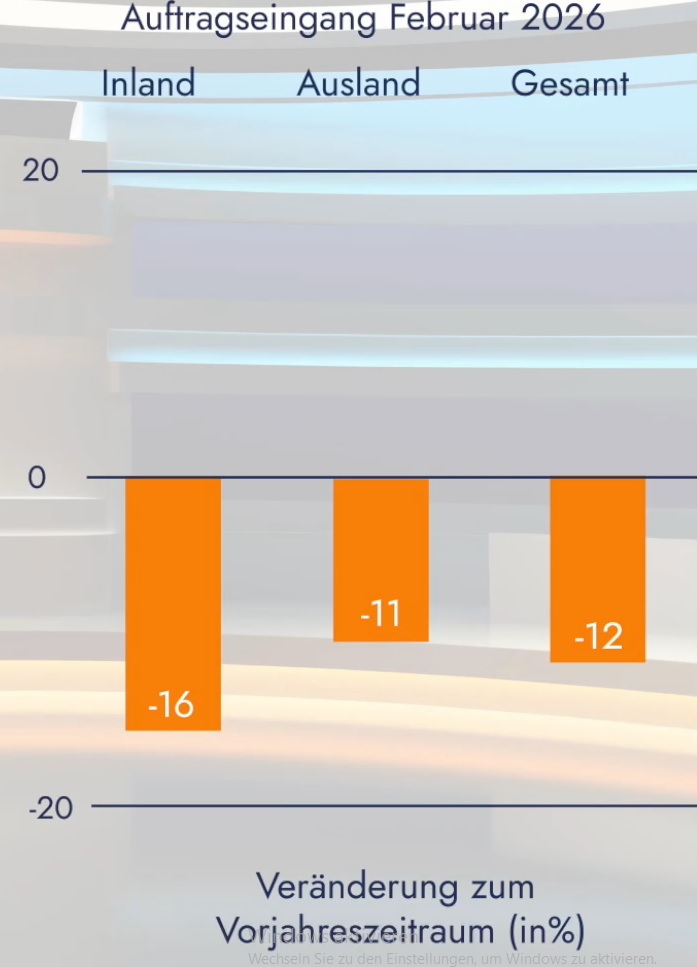

-

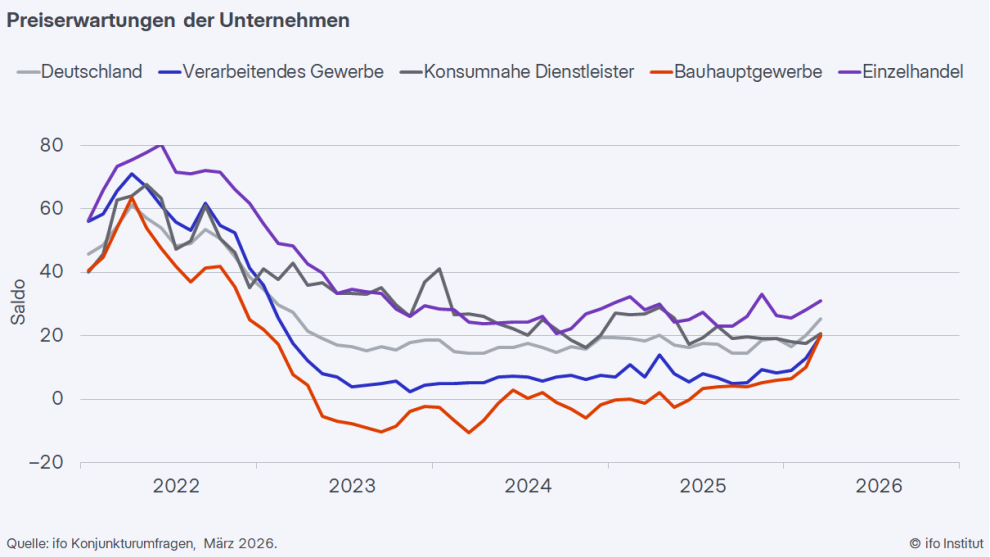

Ifo-Konjunkturumfrage

Unternehmen planen mit höheren Preisen

Deutlich mehr Unternehmen in Deutschland planen mit höheren Preisen.

-

Ann Fairchild neue CEO

Siemens USA unter neuer Leitung

Siemens hat Ann Fairchild zur neuen Geschäftsführerin von Siemens USA ernannt.

-

IO-Link Safety: Sicherheit vernetzt im Feld

Die Automation ändert sich rasant – sicherheitstechnische Anforderungen ebenso. Mit IO-Link Safety entsteht ein neuer Ansatz, Sicherheit direkt ins Feld zu bringen, ohne Umwege über zentrale Steuerungsschichten. In…

-

Mit integrierter Sicherheitstechnik

MDR-Controller für die Intralogistik

Die IP54-geschützten MDR-Controller EP741x von Beckhoff sind je nach Bedarf mit und ohne integrierte Safety verfügbar.

-

Lebensmittelkonformer Oberflächenschutz

Aluminium-Antriebe

Mit NXD Tuph von Nord Drivesystems können Anwender auch in hygienesensiblen Applikationen von Food & Beverage und Primary Packaging die Stärken von Antriebslösungen aus Aluminium nutzen.

-

Feldbuskoppler

Feldbus und Anzeige konsequent integriert

In Profinet-basierten Anlagen übernimmt das PN220 von Motrona die Funktion eines Feldbuskopplers und…

-

Seit März

Hannover Messe erhält eigenen Geschäftsbereich

Zum 1. März hat die Deutsche Messe einen eigenständigen Geschäftsbereich eingerichtet, der sich…

-

Mikko Soirola

Neuer CEO für Elisa Industriq

Mikko Soirola startet als neuer CEO bei Elisa Industriq.

-

Drehkreuz in Südamerika

Wika eröffnet neues Werk in Brasilien

Wika hat Mitte März ein neues Werk am Standort Boituva in Brasilien eröffnet.

-

Professor Dr. Jörn Müller-Quade

Wibu-Systems beruft Kryptografie-Experten in Aufsichtsrat

Wibu-Systems hat Professor Dr. Jörn Müller-Quade in den Aufsichtsrat berufen.

-

IFR stellt Preisträgerinnen vor

Women in Robotics 2026

Um Frauen in der Robotikbranche mehr Sichtbarkeit und Anerkennung zu verschaffen, hat die…

-

Gemeinsam zum vollständig integrierten Automatisierungs-Stack

Salz Automation und Tele vereinbaren Partnerschaft

Salz Automation und Tele Haase Steuergeräte gehen in ihrer Partnerschaft einen entscheidenden Schritt…

-

3D-Druck

Harting eröffnet Zentrum für 3D-Druck

Harting hat in seinem Werk Rahden ein „Center of Competence Additive Manufacturing“ eröffnet.

-

Miniatur-Sensoren realisieren hohe Reichweiten

So weit, so klein

Mit hoher Reichweite, kompaktem Design und optionaler IO-Link-Anbindung eignen sich die Sensoren der…

-

Dank Binnenmarkt

Deutsche Elektroexporte mit Plus auch zum Jahresbeginn

Auch zum Beginn des Jahres 2026 verzeichnete die deutsche Elektroindustrie ein Exportplus: Im…

-

93% verlagern KI zunehmend auf lokale Server

In den letzten zwei Jahren haben 93% befragter Unternehmen einige KI-Workloads zurück auf…

-

Erster Bauabschnitt eingeweiht

Neues Werk in Mexiko für Phoenix Contact

Phoenix Contact hat sein Produktionsnetzwerk auf dem amerikanischen Kontinent ausgebaut. In einem ersten…

-

Festo, Schaeffler und Ziehl-Abegg

Nominierte für Hermes Award stehen fest

Eine unabhängige Jury hat unter den zahlreichen Einreichungen drei Unternehmen für den Hermes…

-

Scada-Plattform Atvise mit Updates

Mehr Sicherheit und Kompatibilität für Scada-Systeme

Mit den Versionen 3.13 und 3.14 erweitert Bachmann Electronic seine Scada-Plattform Atvise um…

-

Beckhoff verbindet Sprachmodelle mit Echtzeitsteuerung

Physical AI: Wenn KI direkt Maschinen steuert“

Ein zentrales Thema für Beckhoff auf der Hannover Messe 2026 ist die Verschmelzung…

-

Vorschau Hannover Messe 2026

KI als produktive Kraft in der Fabrik

Auf der Hannover Messe 2026 vom 20. bis 24. April soll künstliche Intelligenz…

-

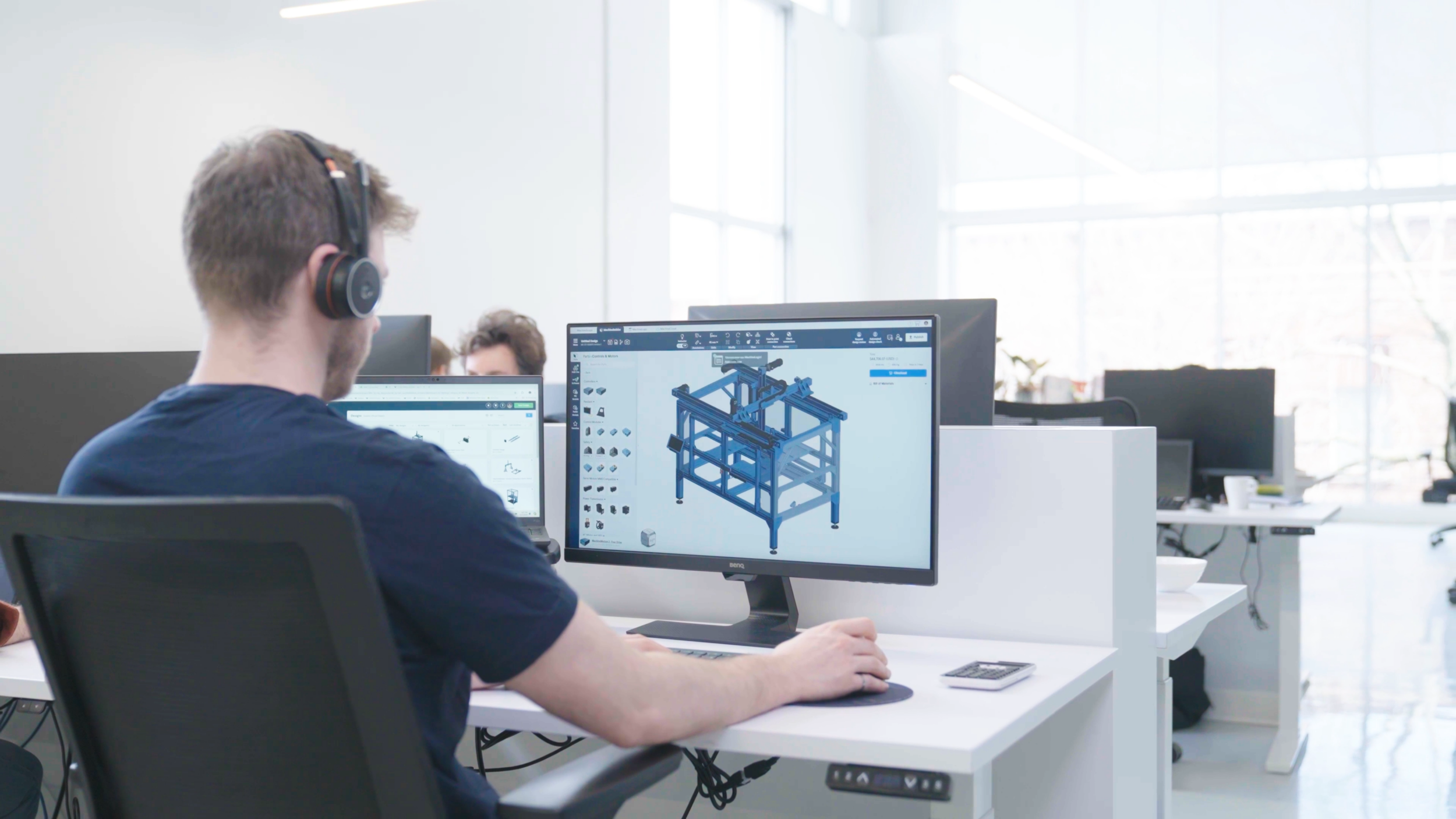

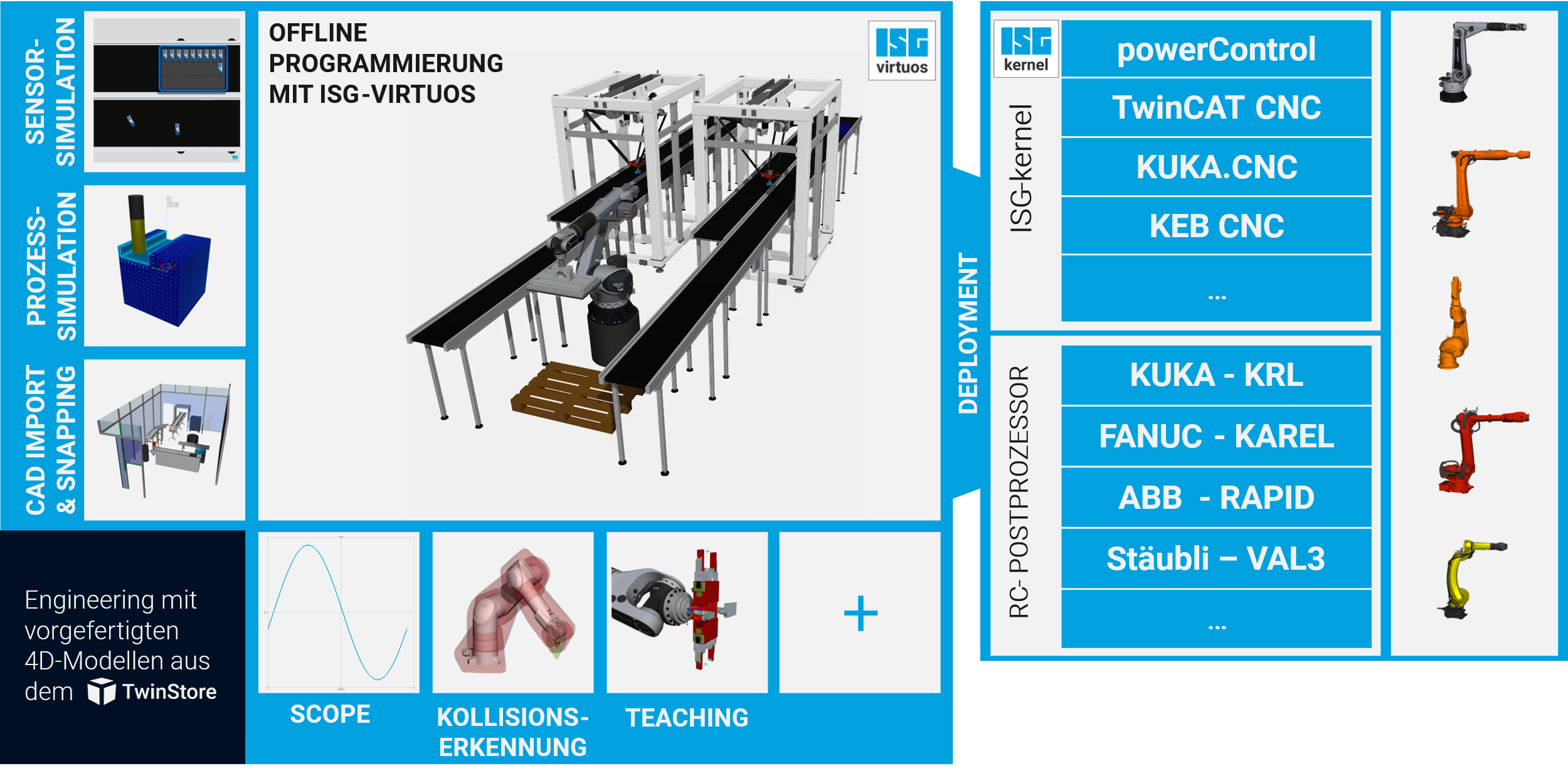

Virtuelle Inbetriebnahme als strategisches Werkzeug

Anforderungen beim Retrofit

Die virtuelle Inbetriebnahme wird im Maschinenbau häufig dafür genutzt, um Steuerungssoftware bereits vor…

-

Warum KI im Mittelstand einen neuen Ansatz braucht

Vom Hype zur Wirkung

Eine aktuelle PwC-Studie unter mehr als 4.400 CEOs weltweit zeigt, dass die erhofften…

-

Klaus Conrad – Unternehmer, Visionär, Möglichmacher

90 Jahre Pioniergeist

Mit 18 Jahren tritt er ins Familienunternehmen ein, mit 40 übernimmt er die…

das könnte sie auch interessieren

-

Very-Small-Form-Factor-Technologie für Next-Generation-Netze

MMC-Stecker für hochdichte Glasfaserverkabelung

-

-

-

Durchgängiges Engineering – von der Planung bis zum Betrieb

Insellösungen überwinden