Seit einigen Jahren konzentrieren sich deshalb die Diskussionen auf ein Ethernet-basiertes Netzwerk, das diese Lücke füllt. Eines dieser Netzwerke ist Ethernet-Powerlink, das 2001 von der österreichischen Firma B&R auf den Markt gebracht wurde. Powerlink ist ein sehr flexibles Echtzeit- Kommunikationsprotokoll. Sein Hauptvorteil ist, dass Devices, Controlled Nodes (CN oder Slaves) und Managing Nodes (MN oder Master) mit Standard-Ethernet-Komponenten, wie 100MBit/s-Ethernet-ähnlicher PHY, Ethernet-MAC-Controllern (EMACs), Kabeln und weiteren Infrastruktur-Komponenten aufgebaut werden können. Nichtsdestotrotz: Zum Erreichen des besten Echtzeitverhaltens, kurzer Verzögerungen und schnellen Antwortzeiten ist es wünschenswert, Hardware-Unterstützung im EMAC zu haben. Eine zweite Anforderung an die CNs ist es, dass sie einen eingebauten Hub besitzen sollten, um Geräte in einer Linientopologie zu verbinden, wie sie konventionelle Feldbusse aufweisen. FPGAs können beide Anforderungen erfüllen. Standard-Ethernet-Hardware Wie bei Ethernet/IP, Modbus TCP und Profinet auch, läuft das offene, Software-basierte Echtzeitkommunikationssystem von Powerlink auf Standard-Ethernet-Hardware, was den Einsatz spezieller Hardware-Komponenten unnötig macht. Die Hersteller der Komponenten müssen deswegen auch keine proprietären Asics entwickeln und zeitaufwendige Tests durchführen. Man kann z.B. Encoder herstellen, die die gleiche Hardware und geeignete Software enthalten. Software-Implementierungen und Neuentwicklungen sind deshalb einfach zu realisieren. Das bedeutet, dass die Verfügbarkeit von Zweit-Lieferanten bei Powerlink besser ist als bei proprietären Systemen. Darüber hinaus erlaubt die offene Struktur von Powerlink einen flexiblen Einsatz der Hardware-Komponenten: Wenn Maschinenbau- oder Fertigungsingenieure ein Gerät, das unter einem anderen Netzwerk läuft in eine Powerlink-Anwendung integrieren wollen, ist alles was sie benötigen, ein zusätzlicher Standard-Controller und ein weiterer Feldbusanschluss. Häufig können für Reparatur- und Wartungsaufgaben in Powerlink-Netzwerken Standard-Diagnose und Messsysteme wie Kabeltester und Netzwerkanalysatoren verwendet werden, wodurch sich die Betriebskosten deutlich verringern. FPGA-Designs für industrielle Echtzeit-Kommunikation sind nicht nur auf Standard-Ethernet beschränkt. Designs für Ethercat, das zwar Standard-Ethernet-Frames benutzt, aber keine Ethernet-MAC-Controller in den Netzwerk-Slaves einsetzen kann, können ebenfalls mit FPGAs implementiert werden. Und obwohl Protokolle wie Ethernet/IP und Modbus TCP die standardmäßigen TriMode-Ethernet-MACs von Xilinx nutzen können, gewinnen Powerlink-Designs durch spezialisierte MAC-Controller viel zusätzliche Leistung. Die Implementierung, die echte 100MBit/s Übertragungsraten erzielt, erfordert weit mehr als nur die einfache Auswahl des geeigneten Übertragungsmediums und der Struktur-Komponenten. Ein großer Teil des Durchsatzes bei Powerlink hängt von den Endpunkten ab. Immer teurere und leistungsfähigere Systeme sind nötig, um mit dem Durchsatz des Netzwerks Schritt zu halten. Leistungsstarke, optimierte FPGA-Lösungen sind dafür der richtige Weg. Deshalb werden nachfolgend mehrere Implementierungsvarianten von Powerlink mit unterschiedlichem Funktionsumfang und unterschiedlicher Komplexität beschrieben. Powerlink- Implementierungsvarianten Ethernet-Powerlink unterscheidet zwischen Echtzeit-Domänen als auch Nicht-Echtzeit-Domänen. Diese Unterscheidung eignet sich besonders für typische Maschinen und Fabrikkonzepte. Er befriedigt auch die steigenden Sicherheitsanforderungen, um Schaden durch eine fehlerhafte Datenübertragung auf den oberen Netzwerk-Hierarchieebenen zu vermeiden. \’Harte\‘ Echtzeitanforderungen werden innerhalb der Echtzeit-Domäne erreicht. Daten, die weniger zeitkritisch sind, werden transparent mit Standard-IP-Frames zwischen der Echtzeit-Domäne und der Nicht-Echtzeit-Domäne geroutet. Die momentane physikalische Ebene ist 100Base-X Fast Ethernet (IEEE 802.3). Alle Netzwerk-Topologien sind dabei möglich. Um eine Topologie aufzubauen empfehlen wir den Einsatz von Hubs in der Echtzeitebene anstelle von Switches, um Verzögerungen und Jitter zu reduzieren. Bild 2 zeigt eine typische Netzwerk-Topologie und die Notwendigkeit für die integrierten Hubs. Powerlink-Ethernet-Hub Das einfachste FPGA-Design, das man in Powerlink-Geräte verwenden kann, ist ein Ethernet-Hub. Die typische Ethernet-Infrastruktur ist eine Stern-Topologie, allerdings erfordern industrielle Netzwerke häufig eine Linien-Topologie. Diese kann erzielt werden, indem man einen Ethernet-Hub in jeden der Powerlink-Knoten implementiert. Bild 3 zeigt einen Controlled-Node, der einen im FPGA implementierten Hub verwendet. Aus Geschwindigkeitsgründen erfordert der Powerlink-Standard eine geringe Signalverzögerung in den Hubs – unter 500ns. Dies kann nur erreicht werden, wenn man den PHY über ein MII-Interface anschließt. Alle anderen Komponenten im Powerlink-Gerät sind Standard-Netzwerk-Komponenten oder Standard-Mikrocontroller. Anstatt eines Mikrocontrollers mit integriertem EMAC kann ein separater Ethernet-MAC-Controller zusammen mit jedem beliebigen Standard-Mikrocontroller eingesetzt werden, um darauf den Powerlink-Stack und die Device-Applikations-Software laufen zu lassen. Powerlink-Ethernet-MAC Im nächsten Schritt wird der wichtigste Teil des VHDL-Codes für die effektive Verarbeitung des Powerlink-Protokolls implementiert: Ein spezieller Ethernet-MAC-Controller, der für Ethernet-Powerlink mit Xilinx-FPGAs optimiert ist. Durch verschiedene spezielle Übertragungs-Buffer und die Möglichkeit automatisch auf Powerlink-Request-Frames in Hardware zu antworten, erreicht man extrem kurze Antwortzeiten. Spezielle Empfangsfilter erlauben das Vorfiltern von Powerlink-Messages durch den MAC-Controller und entlasten die Software von dieser Aufgabe. Diese Filter unterstützen die Vorauswahl von Ethernet-Frames, die von der Verarbeitungs-Software benötigt werden. Basierend auf der verwendeten Einstellung, werden nur diejenigen Frames, die die Filter passieren, in den Empfangs-Buffern gespeichert. Dieses Vorgehen entlastet die CPU davor, Frames zu verarbeiten, die für die Software nicht relevant sind. Der Powerlink-MAC – den wir als PE²MAC bezeichnen – ist eine separate Komponente die mit dem Prozessor über Register (Kontroll- und Status-Information), ein Dual-Port-Memory (Daten-Buffer) und ein Interrupt-Request-Signal verbunden ist. Die Prozessorschnittstelle ist 32Bit breit. Weiterhin wird ein separates Signal geliefert, wenn ein SOC-Paket ankommt. Wird diese Schnittstelle über die FPGA-Pins realisiert, kann selbst ein sehr kleines FPGA ausschließlich als Powerlink-Ethernet-MAC in Verbindung mit jedem Standard-Mikrocontroller verwendet werden. Ein spezieller Powerlink-MAC-Treiber liefert eine optimale Verbindung zur Powerlink-Protokoll-Bibliothek, geschrieben in C, die von Port geliefert wird. Bild 4 zeigt das Design mit einem FPGA basierten EMAC und einer Standard-CPU. Powerlink-Gesamtlösung In größeren FPGAs ist es möglich, das Design zu einer Gesamtlösung auszubauen. Es sind dann nicht nur der Hub und der PE²MAC implementiert, sondern auch die CPU als Soft-Core zur Verarbeitung des Protokolls der höheren Ebenen und der Anwendung. Bild 6 stellt diese FPGA basierte Powerlink-Gesamtlösung für einen Controlled-Node dar. Auf dem CPU-IP-Core laufen C-Programme. Ein spezieller Powerlink-MAC-Treiber bietet eine optimale Verbindung zur Powerlink-Protokoll-Bibliothek von Port. Diese Powerlink-Portokoll-Bibliothek liefert sämtliche erforderlichen Dienste für eine kompatible Kommunikation entsprechend dem Kommunikations-Profil V2.0. Die Powerlink-Protokoll-Bibliothek ist vollständig in Ansi-C geschrieben und kann deshalb mit jedem Ansi-C-kompatiblen Compiler kompiliert werden. Eine mögliche Kombination ist ein eingebetteter Prozessor MicroBlaze von Xilinx und der GNU-gcc-Compiler. In Verbindung mit dem Powerlink-Hub wird damit eine unkomplizierte Verbindung mit einem Powerlink-Netzwerk geboten. Zusätzlich ist damit eine ausgereifte Lösung verfügbar mit technischen Daten (kurze Antwortzeiten, schnelle Reaktion auf Netzwerk-Ereignisse), die die Anforderungen des Powerlink-Standards erfüllen. Die CPU muss den Software-Anteil des Powerlink-Protokolls und die Applikationssoftware bearbeiten. Es ist zu beachten, dass in solchen Single-CPU-Lösungen das Powerlink-Protokoll die Priorität besitzen sollte, um eine gute Netzwerkleistung zu gewährleisten. Der Powerlink-MAC ist zuständig für schnelle Antworten, muss aber mit neuen Daten versorgt werden, wenn die Netzwerk-Zyklen kurz sind. Powerlink- Kommunikationsprozessor Ist die Anwendung selbst sehr zeitkritisch und erfordert Antwortzeiten im unteren Microsekundenbereich (z.B. Steuerschleifen in Bewegungssteuerungen), dann muss man einen Echtzeit- Kommunikations-Co- Prozessor verwenden. Dieses Design besitzt einen Kommunikations- und Applikationsprozessor, die über eine Dual-Port-RAM-Schnittstelle gekoppelt sind. Beide Controller können ihre Echtzeit-Domänen bearbeiten, was zu schnellen Antwortzeiten in beiden Domänen führt. Bild 5 illustriert das Design mit einem FPGA basierten Kommunikations-Co-Prozessor. Das Integrieren des Kommunikations-Co- Prozessors in das FPGA hat viele Vorteile. Das FPGA kann den Hub enthalten (erforderlich für viel Protokolle), den MAC-Controller für das jeweilige Protokoll, einen Standard-Prozessor zur Bearbeitung des Protokoll-spezifischen Daten-Link-Layers sowie das Dual-Port-RAM (DP). Dadurch kann der Kommunikations-Co-Prozessor für Powerlink, Ethercat, Modbus TCP und Ethernet/IP einschließlich CIP-Sync und selbst Profinet RT eingesetzt werden. Zusammenfassung FPGAs eignen sich sehr gut, um leistungsfähige Kommunikationsschnittstellen für industrielle Steuerungsaufgaben zu implementieren, nicht nur – aber speziell – für Ethernet-Powerlink. In Zukunft wird Ethernet Powerlink mit GBit-Ethernet (IEEE 802.3ab) eine Übertragungsrate aufweisen, die zehnmal höher (1000MBit/s) ist als heute. Dies eröffnet neue Perspektiven für die Zukunft, z.B. für komplexe Systeme mit besonderer Produktionsleistung, einer Serie von Steuersystemmodulen, zahlreichen Antrieben und vollständig integrierte Sicherheitsausrüstungen. Diese Techniken sind alle auch auf FPGAs portierbar. Um eine echte 100MBit/s-Leistung zu erreichen, müssen Systeme entwickelt und konfiguriert werden, die einen Datendurchsatz von 100MBit/s im gesamten Netzwerk unterstützen. Dies beinhaltet die Verbesserung der Verarbeitung des Powerlink-Protokolls durch Hardware-Unterstützung, so dass die CPU mehr Zyklen für die Verarbeitung der Applikation zur Verfügung hat (um sicherzustellen, dass unterstützende Software effektiv geschrieben ist) und Chipsätze mit Speichersubsystemen, die die Systemleistung nicht einschränken.

Industrial Ethernet optimal implementieren

-

Infrarotsensor regelt Materialauftrag bei der Plasmabeschichtung

Ultradünne Barriereschichten auf Verpackungen können Lebensmittel oder Medikamente wirksam vor Kontakt mit Sauerstoff, Feuchtigkeit oder Schadstoffen schützen.

-

Neues Mitglied im Wago Management Board

Zum 1. Mai verstärkt Jens Hunecke das Management Board bei Wago als Chief Business Officer des Geschäftsbereichs Interconnection.

-

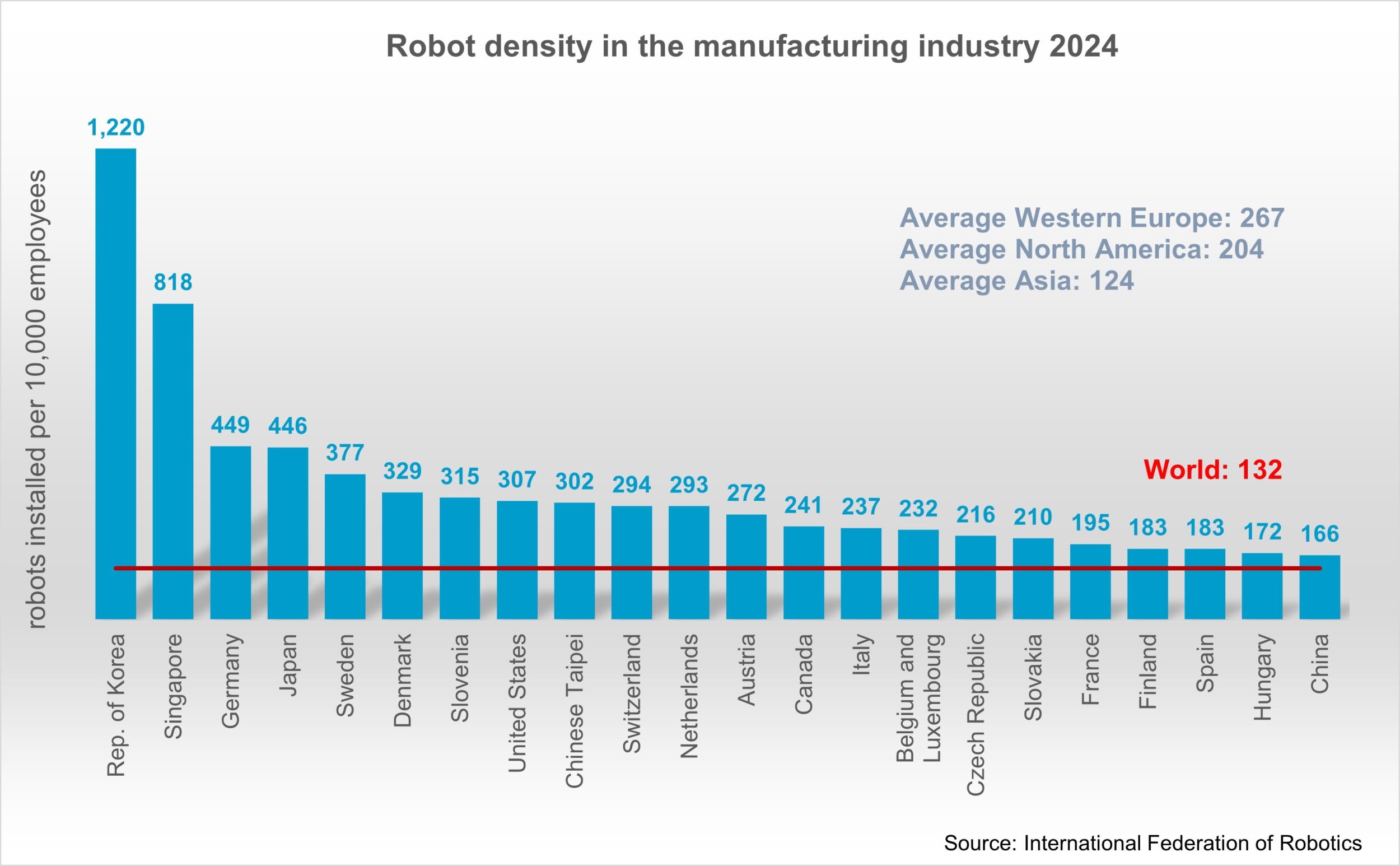

Roboterdichte steigt in Europa, Asien und Amerika

Westeuropa installierte 2024 im verarbeitenden Gewerbe einen Rekord von 267 Industrierobotern pro 10.000 Arbeitnehmern und führt damit im internationalen Automationsrennen vor Nordamerika mit 204 Einheiten und Asien mit…

-

Hochschulausgaben 2024 um 5% gestiegen

Im Jahr 2024 haben die öffentlichen, kirchlichen und privaten Hochschulen in Deutschland insgesamt 79,2 Milliarden Euro für Lehre, Forschung und Krankenbehandlung ausgegeben.

-

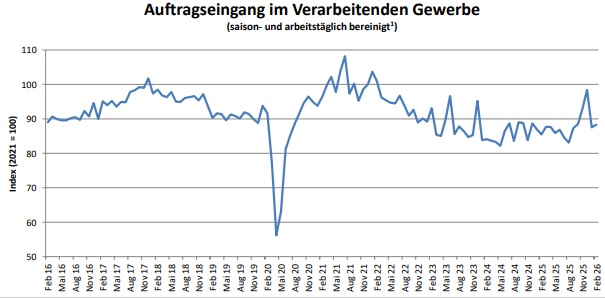

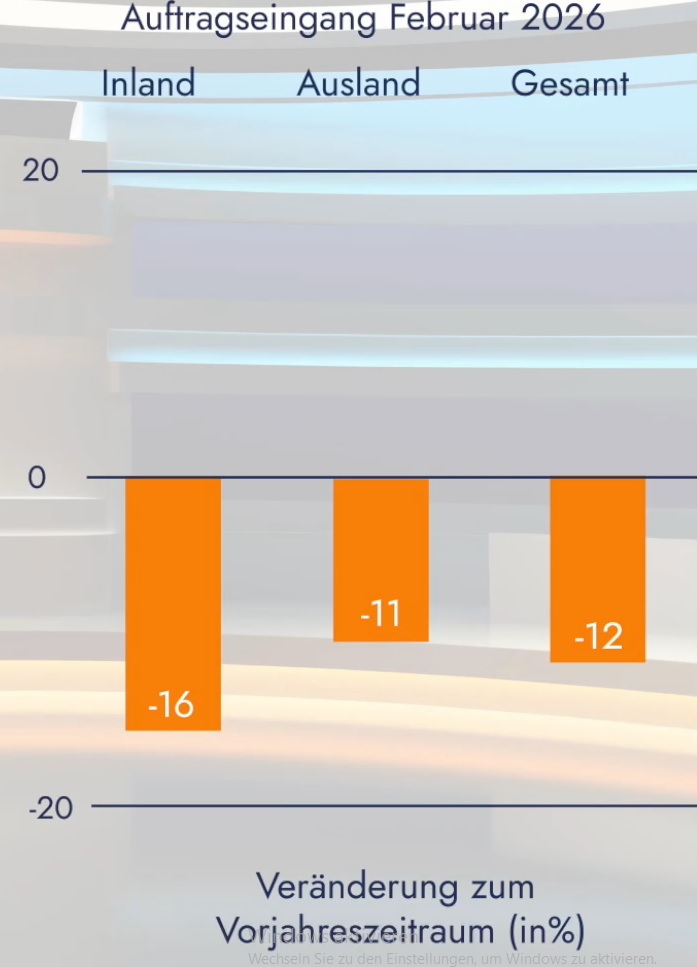

Entwicklung der Auftragseingänge im verarbeitenden Gewerbe für Februar

Nach Angaben des Statistischen Bundesamts legten die Auftragseingänge im Verarbeitenden Gewerbe im Februar 2026 leicht zu: Das Ordervolumen stieg preis-, kalender- und saisonbereinigt gegenüber dem Vormonat um 0,9%.

-

Digitale Prozesse: Mit Ethernet-APL sicher und effizient

Die Digitalisierung der Prozessindustrie schreitet unaufhaltsam voran – und sie stellt neue Anforderungen…

-

Elektromechanisches Fügesystem

Kistler hat mit dem IJSys ein neues Fügemodul entwickelt, das alle Komponenten inklusive…

-

CiA-Vorstand wieder gewählt

Auf der Vollversammlung des Vereins CAN in Automation wurde der amtierende Vorstand bestätigt:…

-

Schmersal gehört 2026 zu den besten Arbeitgebern in Nordrhein-Westfalen

K.A. Schmersal zählt 2026 zu den besten Arbeitgebern in Deutschland.

-

Gute Ergänzung

Der SCHALTSCHRANKBAU und das Thema ’schaltschranklose Automatisierung‘: Wie passt das denn zusammen? So…

-

Wenn Unmanaged Switches Managed Funktionen übernehmen

Plug&Play trifft Priorisierung

Netzwerksegmentierung und Datenflusspriorität sind in der industriellen Automatisierung keine Kür mehr, sondern Pflicht.…

-

Komplexe Bewegungen über High-Level-Sprachen steuern

Es geht auch ohne Echtzeit

Die koordinierte Bewegung mehrerer Achsen – z.B. bei Robotikanwendungen – ist kein neues…

-

Offizielle Eröffnung der Hima-Niederlassungen in Kolumbien und Peru

Die Hima Group baut die Präsenz in Lateinamerika mit der offiziellen Eröffnung neuer…

-

KI perfektioniert Phishing-Angriffe – von personalisierten Mails bis zu Voice Cloning

Wenn Maschinen Vertrauen imitieren

Die KI generiert nicht nur immer neue Hacker-Tools, sondern verbessert die Glaubwürdigkeit von…

-

Interview: Wie neue EU-Regularien Maschinenbauer zu sicheren Kommunikationsarchitekturen zwingen

„Cybersecurity ist heute keine Option mehr“

Mit neuen regulatorischen Vorgaben wie dem Cyber Resilience Act steigt der Druck auf…

-

IO-Link-Safety-Lösungen

Mit der Kombination robuster Sicherheitskomponenten und IO-Link Safety ermöglicht Euchner eine durchgängige, sichere…

-

Im Interview: Wie NI und DataTec den europäischen Testmarkt neu denken

Vom Messgerät zur Datenplattform

Beim Besuch von National Instruments bei DataTec tauschten sich Ritu Favre, President Test…

-

Maßgeschneiderte Schwingungsüberwachung mit IO-Link

Gemeinsam zur Lösung

Steigende Anforderungen an die Überwachung von Schwingförder- und Siebmaschinen erfordern präzise und flexibel…

-

Kompakter Distanzsensor bis 150m

Mit dem OptoNCDT ILR1041-150-IO erweitert Micro-Epsilon sein Laser-Distanzsensoren-Portfolio um ein kompaktes Modell für…

-

Yaskawa strukturiert Führungsspitze in Europa um

Yaskawa hat eine Neustrukturierung der Geschäftsführung in seiner europäischen Zentrale vorgenommen.

-

ABB Robotics ernennt neuen Cluster-Manager für DACH-Region

ABB Robotics hat Marc-Oliver Nandy zum Cluster-Manager für die DACH-Region ernannt.

-

Für sichere Maschinennetzwerke

Industrial Security-Gateway und Maschinenfirewall

Sichere Maschinennetzwerke werden mit den aktuellen Vorgaben der Europäischen Maschinenverordnung und der IEC62443…

-

Skalierbare IPC-Plattform

Spectra bietet mit der MD-3000-Serie von Cincoze eine modulare Embedded-Computer-Plattform an, die speziell…

-

Retrofit für die Industrie 4.0

So lassen sich alte Steuerungen wirtschaftlich OPC-UA-fähig machen

Viele Produktionsanlagen arbeiten noch mit Steuerungen, die seit Jahrzehnten zuverlässig ihren Dienst verrichten.…

das könnte sie auch interessieren

-

Ann Fairchild neue CEO

Siemens USA unter neuer Leitung

-

-

Mit integrierter Sicherheitstechnik

MDR-Controller für die Intralogistik

-

Lebensmittelkonformer Oberflächenschutz

Aluminium-Antriebe